## A REAL-TIME SOFTWARE GNSS RECEIVER DEVELOPMENT FRAMEWORK

**DOUGLAS A. GODSOE**

**April 2010**

# A REAL-TIME SOFTWARE GNSS RECEIVER DEVELOPMENT FRAMEWORK

Douglas A. Godsoe

Department of Electrical and Computer Engineering

University of New Brunswick

P.O. Box 4400

Fredericton, N.B.

Canada

E3B 5A3

April, 2010

© Douglas A. Godsoe, 2010

#### **PREFACE**

This technical report is a reproduction of a dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Electrical and Computer Engineering, April 2010. The research was supervised by Mary Kaye, Department of Electrical and Computer Engineering and Dr. Richard Langley, Department of Geodesy and Geomatics Engineering and funding was provided by the Natural Sciences and Engineering Research Council of Canada.

As with any copyrighted material, permission to reprint or quote extensively from this report must be received from the author. The citation to this work should appear as follows:

Godsoe, D.A. (2010). A Real-Time Software GNSS Receiver Development Framework. Ph.D. dissertation, Department of Electrical and Computer Engineering, published as Technical Report No. 273 by the Department of Geodesy and Geomatics Engineering, University of New Brunswick, Fredericton, New Brunswick, Canada, 256 pp.

## **DEDICATION**

To Pam, for encouraging me to start and supporting me as I finished. Thanks especially to Victoria, for pork chop sandwiches and always making me laugh. And especially to Allan, for being interesting when I needed a distraction, but stop taking all the ammo.

#### **ABSTRACT**

This dissertation provides the architecture and describes the development effort of a modular software-based real-time global navigation satellite system (GNSS) receiver research framework using the Microsoft .NET Framework and the C# programming language. A pipelined signal-processing model is used to address key timing and intermodule synchronization challenges inherent in working with the parallelism required to simultaneously receive and process four or more satellite signals. An extensible interoperability layer provides clearly defined functional interfaces and simplifies the integration of existing hardware and software components with any stage in the signal pipeline. Various aspects of front-end hardware design requirements, as well as new acquisition and tracking mechanisms, are identified and discussed.

The expected benefits of this framework development will be to establish a whole context for software receiver research and to provide a unified view of a software receiver implementation using tools and technologies that encourage the development of diverse feature-rich applications.

#### **PREFACE**

When I began my thesis research I wanted to do work with digital-system design and development. I had a few ideas of specific areas that I intended to explore, such as system on a programmable chip (SoPC) and hardware/software co-design focusing on the practical applications of scientific theory for the development of buildable solutions. The reason I went into engineering in the first place is that I like to see designs implemented; the tangibility of seeing your work constructed and your ideas realized has a large appeal to me.

I needed to find a field of scientific research that used in some practical way the results of digital system design, so I took an interdisciplinary approach of trying to find a problem for a solution technology. I peaked in on the Chemistry department to find out what was going on in that realm with regards to electromagnetic chemical analysis, but as I listened to their explanations, I became uncomfortably aware that while I was familiar with all of the words they were using to describe their work, I had never heard them in that particular order and all together like that before, so I realized that I would be spending most of my time just trying to figure out the pertinent background material and very little on the digital design parts of the problem.

GPS uses a similar spread-spectrum signaling technology used by CDMA cell phones and wireless Ethernet. The basic signals concepts are not that difficult to understand, the solutions combine various aspects of both hardware and software, and as a bonus there's no obvious controls theory to any of it. As far as digital-system applications go, GPS is as

good as any other. Besides, recovering messages from space is kind of cool and people can relate to the work when you tell you're building a GPS thing.

Narrowing down the application area was one thing, but finding a contribution to make is something else. The work couldn't just be a project for the sake of building something; it had to have meaning and value to other people doing similar work. At first I thought of designing and implementing a multi-channel correlator using an FPGA and an assortment of hardware functional blocks, but I soon found out that several dozens of low-cost commercial ICs are available that do this part, already.

In order to get started with some form of GPS research, I looked for the work of others that I could reproduce and possibly enhance or extend. They all required some piece of special hardware or software, or the specific implementation details were so obscured that reproducing the results would be impossible. The really difficult thing in working with spread-spectrum communications is that when things are working properly everything looks like noise, just as it does when things are working improperly, and in practice it's hard to tell the two situations apart.

The idea for the design of the framework came from the realization that there would be a significant benefit to having a reference receiver to act as a starting point for future development work. All of the pieces would be implemented in a way that they could be readily customized to accommodate the integration of components from different sources.

After the initial dissertation proposal, a certain member of the supervisory committee suggested to me that perhaps the project was too big to be done alone—receivers are

complicated things and the reason that researchers tend to concentrate on one area is that it's too much work for one person to do the whole thing by themselves. Not knowing any better, I argued convincingly that it couldn't really be that bad. I should have let myself be talked down from that tree. Nothing works the way the theory in the books describes it does, and to make life worse, the essentials of the receiver are phase-lock and delay-lock loops in mutual feedback control with one another, so I spent hours revisiting the controls material I had hoped to avoid after all—I wanted neither signals or controls and I got both, instead.

In all of the literature, nobody really said how they did it. They have great ideas and algorithms on acquisition, but nothing but hand waving on implementing carrier tracking loops. What information was available was flawed, conflicted, and incomplete. Trying to re-implement someone else's research required having access to their code, their hardware, and their development and test environments. Also, since the work was never a complete receiver, it would have to be integrated with something else in order to get useable results. Each new report of something similar had to be looked at and picked apart to see if it really did what was claimed. Most of them were optimizations of offline receivers.

An array of MATLAB-based offline post-processing applications exists. However, to me, MATLAB obscures the details behind some of the important parts of an implementation. While it makes some things easier, understanding the details of how a particular filter or transform is implemented is important sometimes, and without that understanding applying the results obtained is pretty hard. Also, MATLAB functions on a

Java virtual machine so the performance is wanting, even for offline applications, let alone meeting any sort of real-time target.

The implications of not utilizing MATLAB for the work are numerous and inconvenient. MATLAB provides graphing and plotting capabilities that are time consuming to reproduce. There are also the pieces in the solution that will receive only a one-sentence mention that took many weeks to develop, test and debug. The *Complex* types and the DFT/FFT routines, for example, involved much testing and coding effort and are really only support functions for the receiver framework. There really has been no new work on the FFT since Cooley and Tukey, and what is represented as new is largely plagiarized directly from (1), which itself is adapted from the original version in FORTRAN—two-character variable names and all. No, seriously, go to your favorite search page and search for the following exact phrase and just see how many results are obtained:

"// here begins the Danielson-Lanczos section"

Even though I had tried to avoid signals and controls, learning that the z-transform shares the same generating function as a shift register for the PRN sequences, and that discrete control feedback loops can be analyzed and implemented in a similar manner to digital filters for signal processing was revealing. I've also noticed that the state feedback equations used in controls look like the representation of a Mealy state machine in digital logic systems. There is something intellectually reassuring in these similarities and representational dualities, if for no other reason than it is a form of brain-cell reuse.

I've chosen to include code that supports the theory or ideas as implementation examples. The books that I found most useful were the ones that included coding examples, even if they were in C, FORTRAN, or some flavor of BASIC. These were easy to translate into any language, and they made solid the abstract concepts the text was trying to present. References such as (2) provide no code or example implementations to support the work, and no matter how useful it was at some point in time, the development effort is largely lost forever. C# shares much of the language syntax of C/C++, so examples are included that have little to no dependency on the functions of the .NET base class library (BCL) for operational support. If a BCL function is required in the example, the operations are either well commented or the behavior of the code is evident from the names of the classes and methods invoked.

The Receiver Development Framework described in this thesis is really just a starting point for the exploration of signals-related control applications. The pipeline model and interoperability support features allow for a wide range of ideas to be tested, evaluated, and integrated into a huge variety of working solutions.

There's nothing like a fact you've learned yourself; believe in your own experiences.

#### **ACKNOWLEDGEMENTS**

I'd like to thank my supervisors, Prof. Kaye and Dr. Langley, for their support and guidance over the past few years. Dr. Tervo and Dr. Diduch have always been willing to make themselves available to help me out of the occasional cognitive bind, and for that I am greatly appreciative.

## **Table of Contents**

| DEDICATION                                                              | ii   |

|-------------------------------------------------------------------------|------|

| ABSTRACT                                                                | iii  |

| PREFACE                                                                 | iv   |

| ACKNOWLEDGEMENTS                                                        | ix   |

| Table of Contents                                                       | x    |

| List of Tables                                                          | xiv  |

| List of Figures                                                         | XV   |

| Acronyms and Abbreviations                                              | xxii |

| Chapter 1 Introduction                                                  | 1    |

| <ul><li>1.1 Overview and Background</li><li>1.2 Previous Work</li></ul> |      |

| Chapter 2 GPS Operation                                                 | 14   |

| 2.1 Trilateration                                                       | 14   |

| 2.2 System Overview                                                     |      |

| 2.2.1 System Architecture                                               | 17   |

| 2.2.2 Signals                                                           |      |

| 2.2.3 Transmitted Data                                                  |      |

| 2.2.4 Position Determination                                            |      |

| Chapter 3 Spread-spectrum Fundamentals                                  | 30   |

| 3.1 Spread-Spectrum Types                                               | 30   |

| 3.1.1 Frequency Hopping                                                 | 31   |

| 3.1.2 Direct Sequence                                                   |      |

|       | 3.2   | Transmitter and Receiver Architecture              | 33  |

|-------|-------|----------------------------------------------------|-----|

|       | 3.    | .2.1 Modulation                                    | 33  |

|       |       | .2.2 Demodulation                                  |     |

|       |       |                                                    |     |

|       | 3.3   | PRN Sequences and Generators                       | 35  |

| Chant | or 1  | Object-Oriented Analysis and Design                | 37  |

| Спарі | .CI 4 | Object-Oriented Analysis and Design                |     |

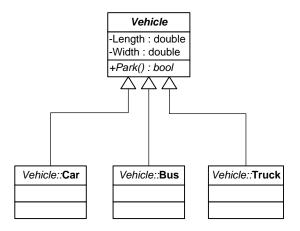

|       | 4.1   | Encapsulation                                      | 37  |

|       | 4.2   | Inheritance                                        | 41  |

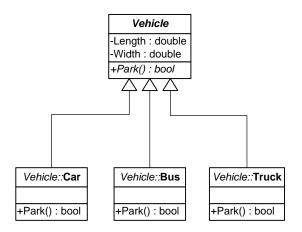

|       | 4.3   | Polymorphism                                       | 42  |

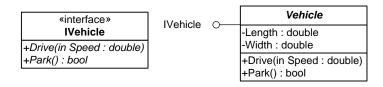

|       | 4.4   | Special Items                                      |     |

| Chapt | er 5  | Real-time Systems                                  | Δ7  |

| Chapt | .01 5 | Real time bystems                                  |     |

|       | 5.1   | Definition of Real-time                            | 48  |

|       | 5.2   | Applications, Processes, and Threads               | 52  |

|       | 5.3   | Scheduling                                         | 55  |

|       | 5.4   | Synchronization                                    | 64  |

|       | 5.5   | Architectural Modeling and Languages for Real-time | 68  |

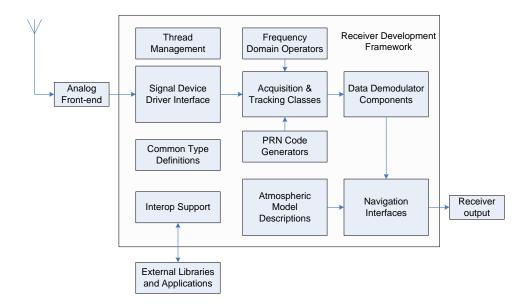

| Chapt | er 6  | Development Framework Overview                     | 77  |

| •     |       | Receiver Framework Architecture Diagram            |     |

|       |       |                                                    |     |

|       |       | Pipeline Processing Model                          |     |

|       |       | .2.1 Synchronous Pipeline                          |     |

|       |       | .2.2 Asynchronous Pipeline                         |     |

|       |       | .2.3 Pipeline Component                            |     |

|       |       | .2.4 Pipeline Container                            |     |

|       |       | .2.5 Phase-Lock Loop Pipeline Component            |     |

|       | 6.    | .2.6 Delay-Lock Loop                               | 103 |

|       |       | .2.7 Numerically Controlled Oscillator             |     |

|       |       | .2.8 Data Demodulator                              |     |

|       |       | .2.9 Signal Controller                             |     |

|       | 6.    | .2.10 PRN Code Generation                          | 114 |

|       | 6.3   | Common Types                                       | 116 |

|       | 6.    | .3.1 Complex                                       | 117 |

|       | 6.    | .3.2 DFT                                           | 117 |

|       | 6.    | .3.3 FFT                                           | 117 |

|       | 6.    | .3.4 Filter Classes                                | 118 |

|       |       | 3.5 Frequency                                      | 118 |

| Chapter 7 Interoperability Support                          | 119 |

|-------------------------------------------------------------|-----|

| 7.1 Interoperability Requirements                           |     |

| 7.2 Interoperability Layered Model                          |     |

| 7.3 Interoperability Scenarios                              | 125 |

| 7.3.1 Single Process                                        | 126 |

| 7.3.2 Interprocess                                          | 127 |

| 7.3.3 Interprocess with Remote Execution                    | 129 |

| Chapter 8 Signal Source Device Driver Interface             | 131 |

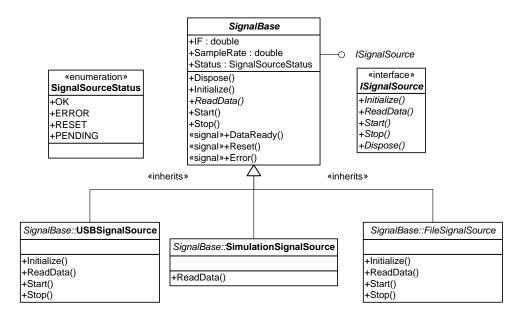

| 8.1 Layered Device Driver Approach                          | 132 |

| 8.1.1 Signal Source Device Interface                        | 140 |

| 8.1.2 Signal Source Base Class                              |     |

| 8.1.3 Signal Source Derived Classes                         | 143 |

| 8.2 Device Interface State Models                           | 143 |

| 8.2.1 Signal Source System State Model                      | 143 |

| 8.2.2 State Model for USB Signal Source                     |     |

| Chapter 9 Acquisition and Tracking                          | 147 |

| 9.1 Acquisition                                             | 147 |

| 9.2 Tracking                                                |     |

| Chapter 10 Reference Implementation Results                 | 152 |

| 10.1 Pipeline Testing Configuration                         | 153 |

| 10.2 Real-time Performance Evaluation                       |     |

| 10.3 Interoperability Component Integration                 |     |

| Chapter 11 Conclusion                                       | 182 |

| Chapter 11 Conclusion                                       | 102 |

| Appendices                                                  | 188 |

| Introduction to the Appendices                              | 188 |

| Appendix A— 3 <sup>rd</sup> -party Toolkit Interoperability |     |

| Library Background and History                              | 189 |

| Component Object Model                                      |     |

| The .NET Framework                                          |     |

| Integration of GPSTk                                        |     |

| Additional Features                                         | 207 |

| Appendix B— Tracking-loop Control Theory | 211 |

|------------------------------------------|-----|

| Appendix C— Finite Fields and SSRGs      | 220 |

| Appendix D— Background Signals Theory    | 238 |

|                                          |     |

| References                               | 245 |

|                                          |     |

| Index                                    | 256 |

|                                          |     |

|                                          |     |

Curriculum Vitae

## **List of Tables**

| Table 6-1—Typical PLL discriminator functions                                                               |

|-------------------------------------------------------------------------------------------------------------|

| Table 6-2—Typical DLL discriminator functions                                                               |

| Table 10-1—Visible satellites extracted from file captured on June 5, 2009 at 13:16 UTC 162                 |

| Table 10-2—Visible satellites extracted from file captured on June 10, 2009 at 15:52 UTC 163                |

| Table 10-3—Performance testing on 40 seconds of data from the SiGe EK3 front-end hardware                   |

|                                                                                                             |

| Table 10-4—Satellite tracking results with a simulated signal                                               |

| Table 10-5—Performance testing on 40 seconds of data from the simulated signal model 172                    |

| Table C-1—The equivalence between XOR and multiplication with $\{0, 1\} \leftrightarrow \{+1, -1\}$ mapping |

|                                                                                                             |

| Table C-2—Example 7-bit autocorrelation calculations. Each row represents one additional bit                |

| delay                                                                                                       |

| Table C-3—Correlation results                                                                               |

| Table D-1—Relationships between the properties of the time and frequency domains                            |

## **List of Figures**

| Figure 2-1—Trilateration: Determining the range to three transmitters at known locations permits |

|--------------------------------------------------------------------------------------------------|

| an observer to calculate their position, point P                                                 |

| Figure 2-2—GPS Frequencies and Codes: Note that the L5 frequency and the L2C and M codes         |

| are only active on some satellites                                                               |

| Figure 2-3—C/A Code Generation: The C/A code is formed by the product of two sequences, G1       |

| and G2                                                                                           |

| Figure 2-4—GPS Navigation message structure                                                      |

| Figure 2-5—Fixing a position requires finding the pseudoranges to at least four satellites 28    |

| Figure 2-6—GPS receiver block diagram                                                            |

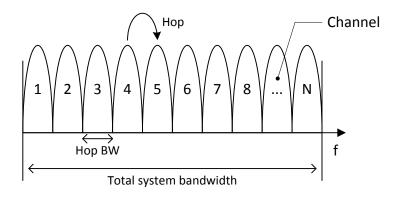

| Figure 3-1—Frequency Hopping Spread Spectrum: The total bandwidth available is divided into      |

| multiple channels, and each channel is occupied randomly in turn by the modulated carrier        |

| signal for a short interval of time                                                              |

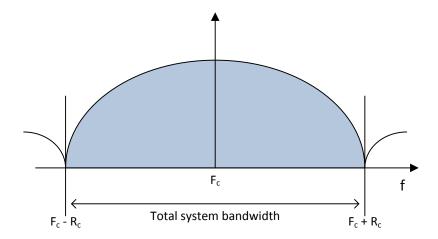

| Figure 3-2—Direct Sequence Spread Spectrum: The transmitted carrier frequency determines the     |

| position of the center of the spectrum, while the width (spreading) is determined by the chip    |

| rate (Rc)                                                                                        |

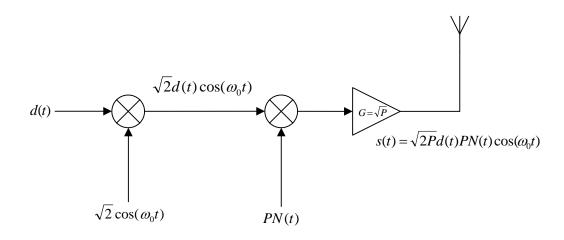

| Figure 3-3—BPSK DSSS Transmitter: The input data, d(t), is combined with the carrier and then    |

| binary phase shift keyed with the pseudo-noise sequence                                          |

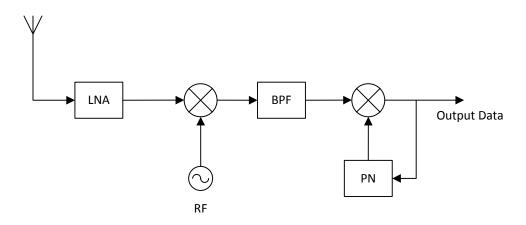

| Figure 3-4—Direct Sequence BPSK receiver model                                                   |

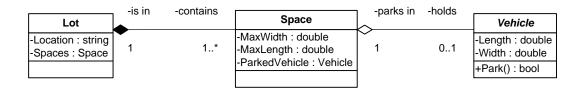

| Figure 4-1—Static UML object model for a parking application                               | 39           |

|--------------------------------------------------------------------------------------------|--------------|

| Figure 4-2—UML object-model showing inheritance                                            | 42           |

| Figure 4-3—Each class derived from vehicle implements a specialized polymorphic P          | ark method   |

|                                                                                            | 43           |

| Figure 4-4—An interface declaration and a class that implements it                         | 45           |

| Figure 6-1—Block diagram model of the Receiver Development Framework                       | 80           |

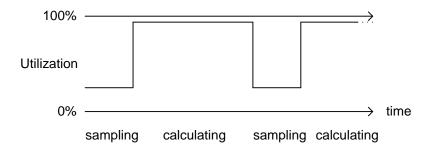

| Figure 6-2—CPU Workload with a capture-then-process signal processing approach.            | 84           |

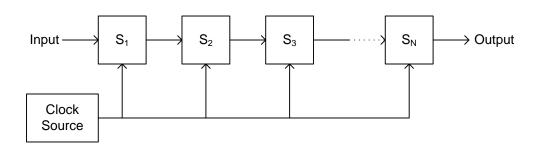

| Figure 6-3—Pipeline structure with a common clock                                          | 85           |

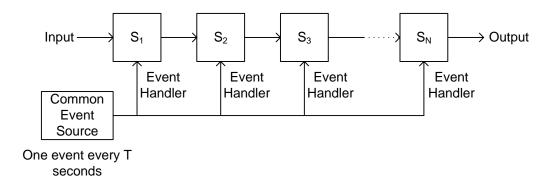

| Figure 6-4—Event-driven synchronous pipeline process                                       | 86           |

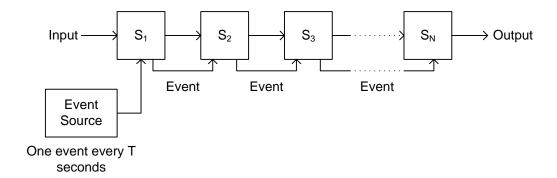

| Figure 6-5—Asynchronous software pipeline model using event coupling between such          | ecessive     |

| stages                                                                                     | 88           |

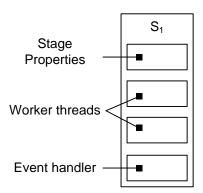

| Figure 6-6—Pipeline stage 1 event-handler structure with separate worker threads           | 89           |

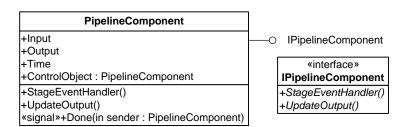

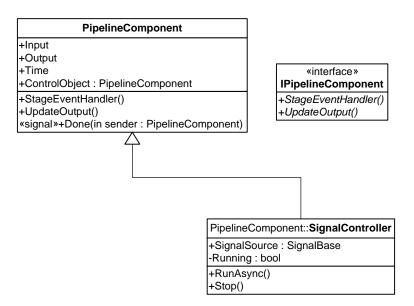

| Figure 6-7—Pipeline component object model                                                 | 90           |

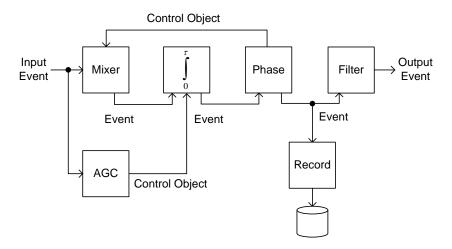

| Figure 6-8—Example pipeline configuration showing feed-forward and feedback configuration. | trol objects |

| with parallel pathways                                                                     | 92           |

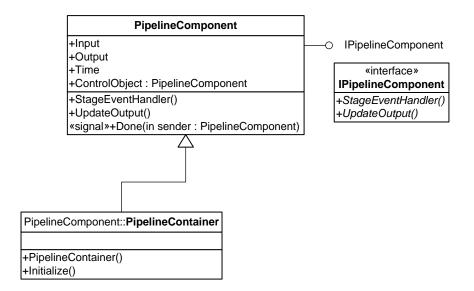

| Figure 6-9—PipelineContainer class diagram                                                 | 95           |

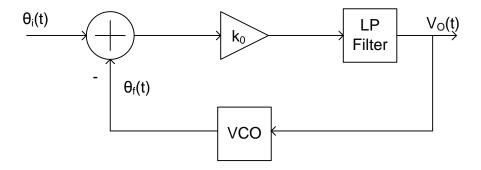

| Figure 6-10—A basic phase-lock loop                                                        | 97           |

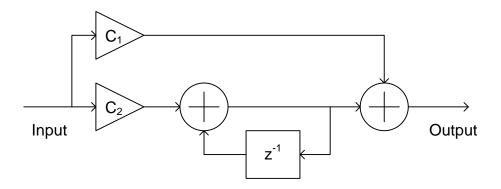

| Figure 6-11—PI controller as the filter function for a PLL                                 | 97           |

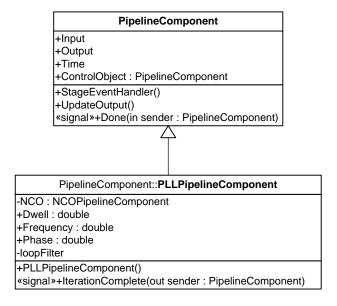

| Figure 6-12—PLLPipelineComponent class diagram                                                   |

|--------------------------------------------------------------------------------------------------|

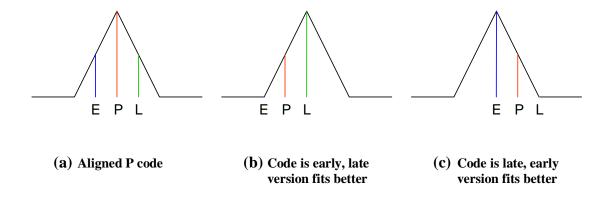

| Figure 6-13—DLL E, P, L correlator outputs under on-time (a), early (b), and late conditions (c) |

|                                                                                                  |

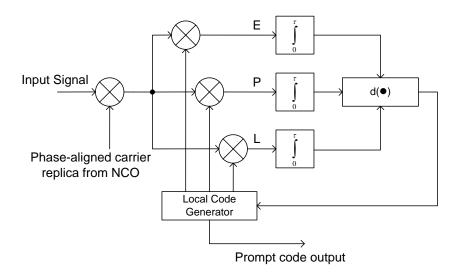

| Figure 6-14—DLL correlator block diagram                                                         |

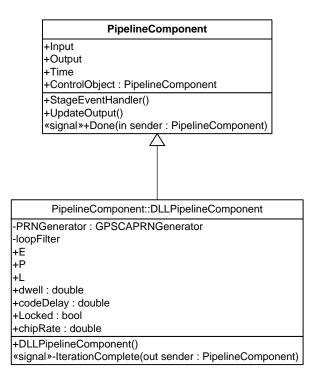

| Figure 6-15—DLLPipelineComponent class diagram                                                   |

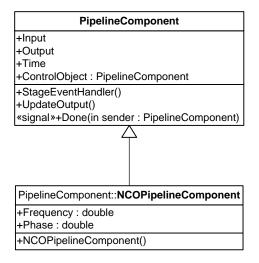

| Figure 6-16—NCOPipelineComponent class diagram                                                   |

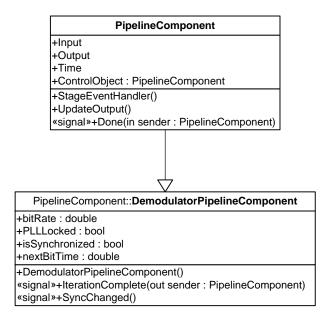

| Figure 6-17—UML static object model for the demodulator component                                |

| Figure 6-18—SignalController object model                                                        |

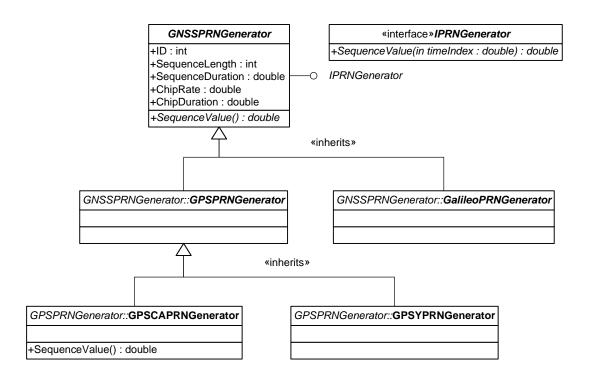

| Figure 6-19—UML static object model for PRN code generators                                      |

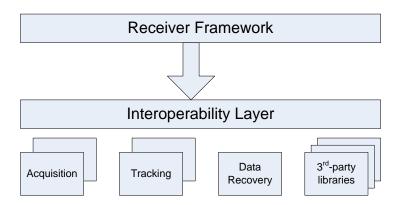

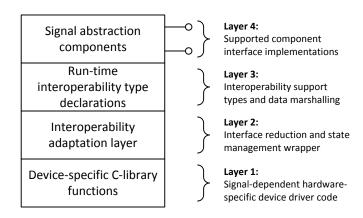

| Figure 7-1— Interoperability Layer                                                               |

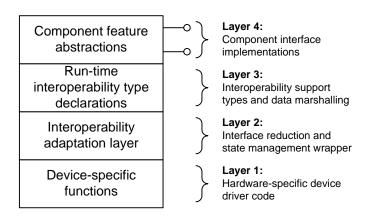

| Figure 7-2—Layered Interoperability Model                                                        |

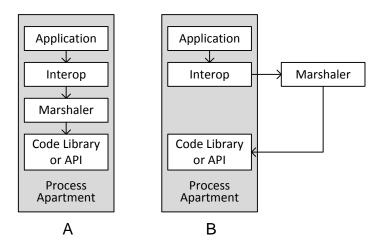

| Figure 7-3—Single process interoperability function call: custom marshaler in A, system          |

| marshaler in B                                                                                   |

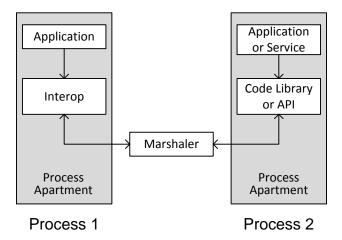

| Figure 7-4—Interprocess with common data types and system marshaler                              |

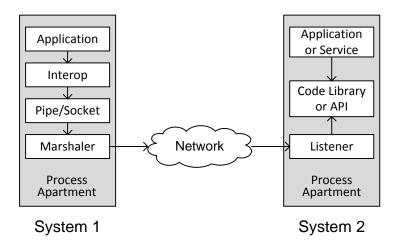

| Figure 7-5—Interprocess interoperability between two systems with remote code execution 129      |

| Figure 8-1—Layered Device Driver Model                                                           |

| Figure 8-2—LibUSB library function for starting a USB device                                     |

| Figure 8-3—Exported USB functions from Layer-2                                                   |

| Figure 8-4—Implementation of the Layer-2 USB function for device initialization          | . 134 |

|------------------------------------------------------------------------------------------|-------|

| Figure 8-5—Layer-4 device wrapper declaration for the GN3S device driver                 | . 135 |

| Figure 8-6—Layer-4 wrapper code implementation for the GN3S device driver initialization |       |

| sequence                                                                                 | . 136 |

| Figure 8-7—Abstract signal base class implementation UML static structure diagram        | . 137 |

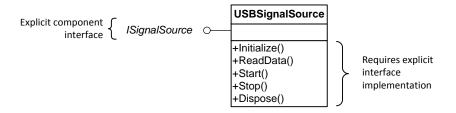

| Figure 8-8—Explicit interface implementation                                             | . 139 |

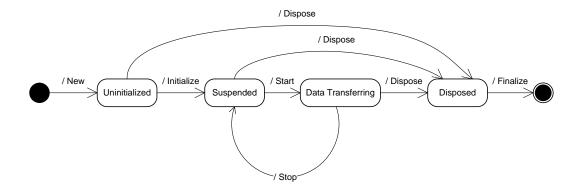

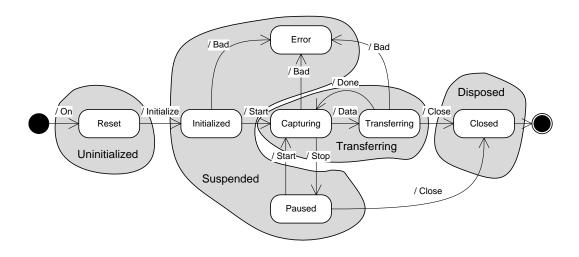

| Figure 8-9—Generic signal source UML Statechart model                                    | 143   |

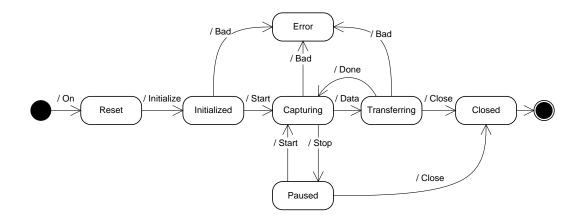

| Figure 8-10—USB signal source internal state model                                       | . 145 |

| Figure 8-11—USB device state model as mapped into the system state model                 | . 145 |

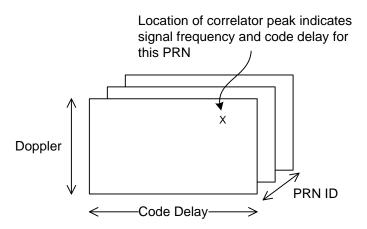

| Figure 9-1—Software-based signal determination                                           | 148   |

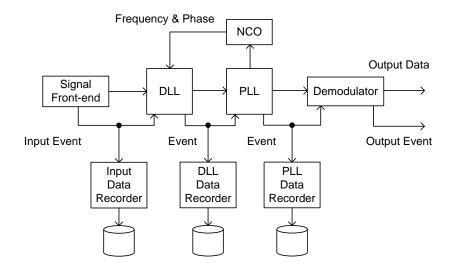

| Figure 10-1—Tracking pipeline configuration used for testing                             | 154   |

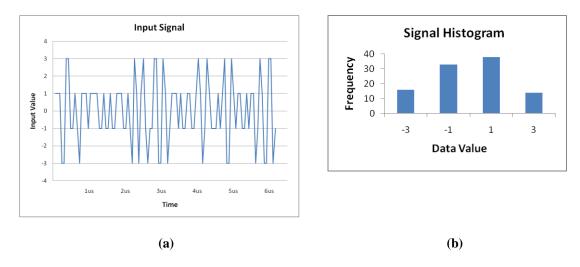

| Figure 10-2—Time-domain view of input signal source (a) and input signal histogram (b)   | . 157 |

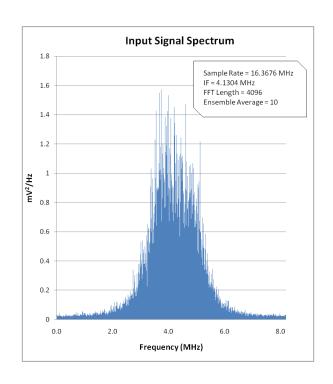

| Figure 10-3—Frequency-domain view of input signal                                        | . 158 |

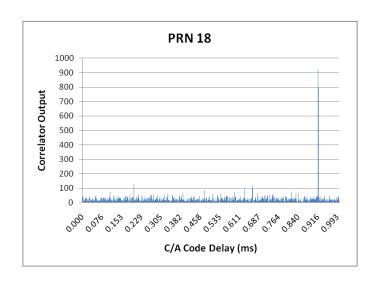

| Figure 10-4—Correlation peak for PRN#18 detection                                        | 159   |

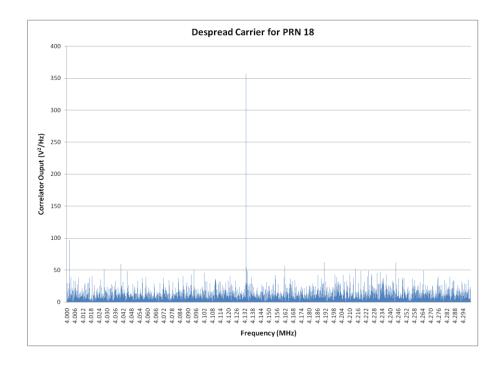

| Figure 10-5—Frequency-domain view of recovered carrier for PRN #18                       | . 159 |

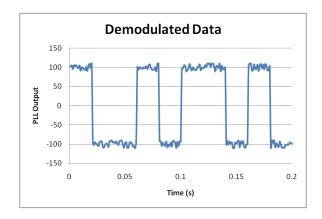

| Figure 10-6—Navigation data signal from PLL output                                       | 161   |

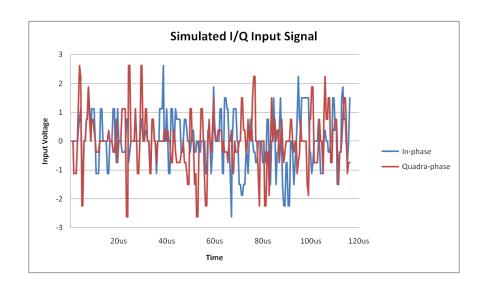

| Figure 10-7—Input I/Q signal from the simulated signal source used for testing           | . 167 |

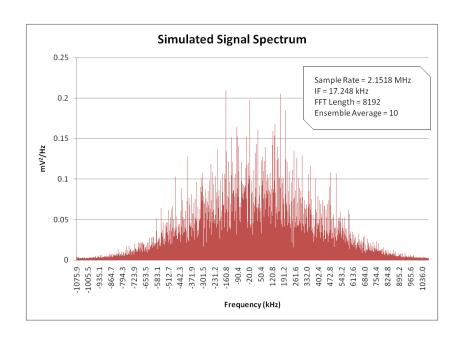

| Figure 10-8—Double sided spectrum for simulated signal source                            | . 168 |

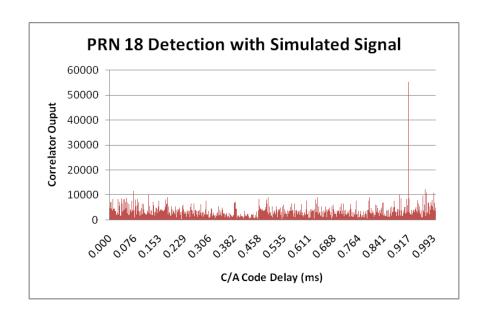

| Figure 10-9—Circular correlation peak detection using simulated signal source                                                    |

|----------------------------------------------------------------------------------------------------------------------------------|

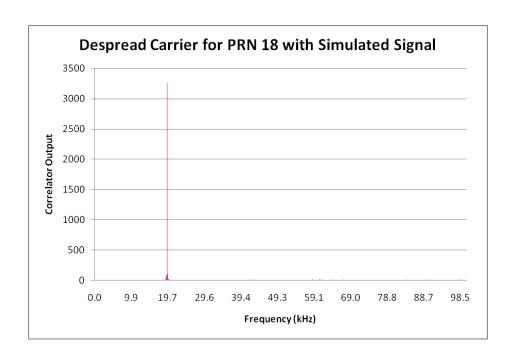

| Figure 10-10—Frequency-domain view of carrier using the simulated signal source                                                  |

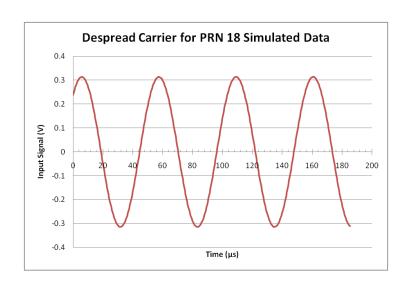

| Figure 10-11—Time-domain view of recovered carrier using the simulated signal source 171                                         |

| Figure 10-12—Precompiled header file stdafx.h used for the GNURadioParts library project 176                                     |

| Figure 10-13—Header file GNURadioParts.h with the <i>UpdateOutput()</i> function exported from the GNURadioParts library project |

| Figure 10-14—CPP source file GNURadioParts.cpp showing the <i>UpdateOutput()</i> function implementation                         |

| Figure 10-15—CPP source file DllMain.cpp with the gr_pll_refout_cc instance initialization 179                                   |

| Figure 10-16—C# source file GNURadioWrapper.cs that imports the GNURadioParts library 179                                        |

| Figure 10-17—C# source file GNUPLLPipelineComponent.cs for invoking the  GNURadioWrapper <i>UpdateOutput()</i> static method     |

| Figure 10-18—PipelineContainer PLL member declaration and initialization for  GNUPLLPipelineComponent class integration          |

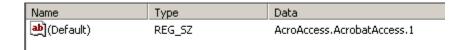

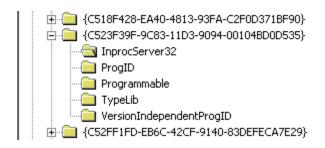

| Figure A-1—Acrobat Access system registry entry                                                                                  |

| Figure A-2—Acrobat Access version specific program ID                                                                            |

| Figure A-3—Acrobat Access class ID key                                                                                           |

| Figure A-4—Acrobat Access class ID value                                                                                         |

| Figure A-5—Acrobat Access InprocServer32 sub-key                                                                                 |

| Figure A-6—  | -Acrobat Access executable file registry entry                            | 195 |

|--------------|---------------------------------------------------------------------------|-----|

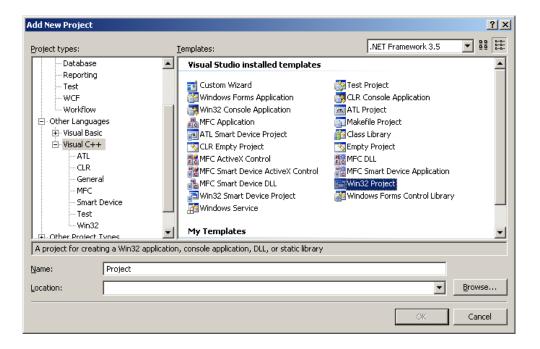

| Figure A-7—  | -Visual Studio 2008 new project dialog                                    | 200 |

| Figure A-8—  | -Visual Studio 2008 new project dialog                                    | 201 |

| Figure A-9—  | -Exported code symbol C macro                                             | 201 |

| Figure A-10- | —C++ class code exported using API macro                                  | 202 |

| Figure A-11- | —Dialog for adding a DLL module export definition file                    | 203 |

| Figure A-12- | —Definition file exported symbols                                         | 203 |

| Figure A-13- | —API Macro exported symbols using C naming styles                         | 204 |

| Figure A-14- | —C++ exported function implementation                                     | 205 |

| Figure A-15- | —Exported symbols using C naming styles, without the use of the API macro | 205 |

| Figure A-16- | —Exported symbols using C naming styles                                   | 205 |

| Figure A-17- | —C# class for accessing the functions exported from the GPSTk library     | 206 |

| Figure A-18- | —C# event handler that invokes functions from the external GPSTk library  | 207 |

| Figure A-19- | —C++ code for initializing a persisted class instance                     | 209 |

| Figure A-20- | —C++ code for accessing a persisted class instance                        | 209 |

| Figure B-1—  | -PLL feedback control model                                               | 213 |

| Figure B-2—  | -Sample and hold representation                                           | 214 |

| Figure R-3—  | -PLL 1 <sup>st</sup> -order filter                                        | 215 |

| Figure B-4—A simple transfer function                                               | 215 |

|-------------------------------------------------------------------------------------|-----|

| Figure B-5—C# code for implementing the 1 <sup>st</sup> -order filter of Figure B-3 | 217 |

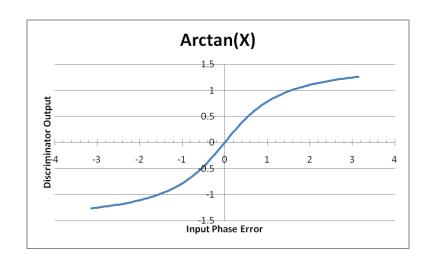

| Figure B-6—Arctangent discriminator function over the range $[-\pi, \pi]$           | 218 |

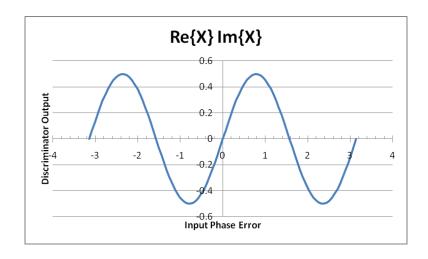

| Figure B-7—Product discriminator function over the range $[-\pi, \pi]$              | 218 |

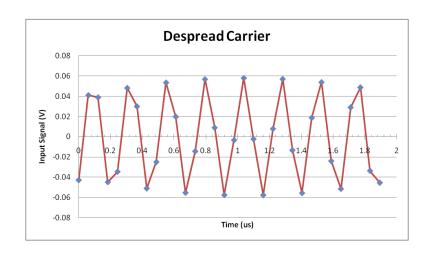

| Figure B-8—Recovered carrier waveform, after code removal                           | 219 |

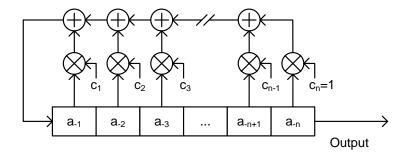

| Figure C-1—Fibonacci implementation of P(x)                                         | 223 |

| Figure C-2—Galois implementation of P(x)                                            | 224 |

| Figure C-3—GNSS implementation of P(x)                                              | 224 |

| Figure C-4—SSRG configuration                                                       | 227 |

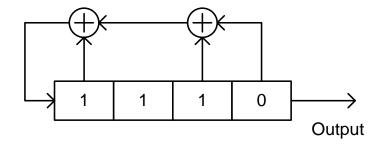

| Figure C-5—Example shift register                                                   | 229 |

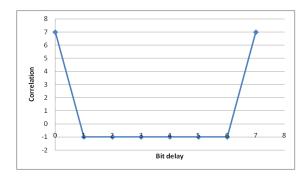

| Figure C-6—Non-normalized autocorrelation                                           | 232 |

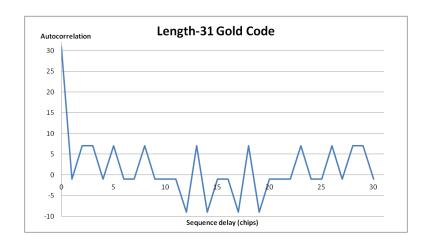

| Figure C-7—Length-31 Gold code autocorrelation function                             | 233 |

| Figure C-8—GPS C/A-code generator configuration                                     | 234 |

## **Acronyms and Abbreviations**

| ADL   | Architectural description language                    |

|-------|-------------------------------------------------------|

| AGC   | Automatic gain control                                |

| API   | Application Programming Interface                     |

| BCL   | Base class library                                    |

| BPF   | Band-pass filter                                      |

| BPSK  | Binary Phase-shift Keying                             |

| C/A   | Coarse Acquisition                                    |

| CCS   | CORBA Component System                                |

| CCS   | Calculus of communicating systems                     |

| CDMA  | Code-division Multiple-access                         |

| CISC  | Complex instruction set computer                      |

| CORBA | Common Object Resource Broker Architecture            |

| CPU   | Central processing unit                               |

| CSP   | Communicating sequential processes                    |

| DDLL  | Discrete delay-lock loop                              |

| DFT   | Discrete Fourier Transform                            |

| DLL   | Delay-lock loop or Dynamic-link library               |

| DPLL  | Discrete phase-lock loop                              |

| DSP   | Digital Signal Processing or Digital Signal Processor |

| DSSS  | Direct-sequence spread-spectrum                       |

| FFT   | Fast Fourier Transform                                |

| FHSS  | Frequency hopped spread-spectrum                      |

| FPGA | Field Programmable Gate Array                |

|------|----------------------------------------------|

| GNSS | Global Navigation Satellite System           |

| GPS  | Global Positioning System                    |

| HDL  | Hardware description language                |

| HPET | High-performance event timer                 |

| HTTP | Hyper-text transfer protocol                 |

| I, Q | In-phase (signal), Quadrature-phase (signal) |

| LNA  | Low-noise amplifier                          |

| LPF  | Low-pass filter                              |

| MMX  | Multimedia extensions                        |

| NCO  | Numerically controlled oscillator            |

| ODBC | Open database connectivity                   |

| OLE  | Object linking and embedding                 |

| OMT  | Object modeling technique                    |

| 0-0  | Object-oriented                              |

| OS   | Operating system                             |

| PLL  | Phase-lock loop                              |

| PRN  | Pseudo-random noise                          |

| RF   | Radio-frequency                              |

| RISC | Reduced instruction set computer             |

| RPC  | Remote Procedure Call                        |

| RUP  | Rational Unified Process                     |

| SDR  | Software Defined Radio                       |

| SIMD | Single instruction multiple data             |

| SOPC | System on programmable chip                  |

| SSE   | Streaming SIMD extensions                  |

|-------|--------------------------------------------|

| SSRG  | Sequential serial shift register generator |

| TOA   | Time of arrival                            |

| UML   | Unified modeling language                  |

| VHDL  | VHSIC hardware description language        |

| VHSIC | Very high-speed integrated circuit         |

| XML   | Extensible mark-up language                |

#### **Chapter 1 Introduction**

There are many expected and anticipated advantages of software Global Navigation Satellite System (GNSS) receivers over conventional hardware implementations. Among these benefits are lower cost, greater flexibility, easier updating or upgrading mechanisms, and better adaptability for supporting new signals and frequencies. Software receivers serve as fertile ground for researchers exploring the exciting possibilities of the development and testing of new signal processing techniques and ideas. Satisfying the computational requirements for a real-time software receiver has focused much of the current research and development effort on innovative algorithms aimed at reducing the necessary processing complexity. For the purposes of proof-of-concept testing, many of these ideas have been demonstrated using some combination of Field Programmable Gate Arrays (FPGAs) and commercial Digital Signal Processors (DSPs) with software written in assembly language. PC-based demonstrations that take advantage of the MMX/SSE (streaming SIMD—single instruction, multiple data—extensions) instruction sets provided by the Pentium-4 microprocessor have required the use of optimized assembler code for their implementations.

While perhaps reconfigurable, Hardware Definition Languages (HDLs), such as VHDL (very high speed integrated circuit hardware description language) or Verilog, are intended to describe hardware operations and are not widely considered to be software as the compiled binaries are not executed on a general purpose processor. Solutions based on a System on a Programmable Chip (SoPC) philosophy, using one or more soft-core

processors in combination with various application specific logic blocks, bring the features and performance benefits of both hardware and software. However, they also suffer all the combined development challenges of hardware and software systems, as well, in that they are often difficult to customize, requiring the support of a mix of non-integrated vendor-specific tools and components. Furthermore, solutions built from specialized DSP chipsets using hand-optimized assembly languages and esoteric development tools require specialized software skill-sets to reproduce. These systems represent more of a one-off customized hardware implementation approach and generally fail to satisfy the adaptability and flexibility benefits expected from software receivers.

Using readily available tools and high-level programming languages makes the technology more accessible to would-be system implementers and brings the desired software receiver goals closer to realization. Beneficial side-effects include having access to larger data storage devices, network connectivity and XML-based web-service integration, links to GIS and mapping information, and support for rich application functionality that is difficult to provide through low-level code only.

Eventually, everything falls out from having the local code and carrier precisely aligned with the received signal. As developed and tested, with a 2.4 GHz Pentium 4 Quad-core processor working in conjunction with a front-end sampler sampling at approximately 16 MHz, it first appears that there should be enough processing resources to manage the amount of work required. The processor clock is roughly 150x faster than the sampling-rate, which really implies, though, that there is only 150 clock-cycles worth of time in order to process one sample. The situation worsens when the level of application parallelism is not ideal (Chapter 5), and the multiple-processors are doing

other work unrelated to processing the input signal. Work such as running the operating system, responding to user input, and memory management require clock-cycles that need to be accounted for.

A real-time solution will require the use, management, and synchronization of multiple threads of processing. The synchronization and scheduling problems are non-trivial issues that cannot be simply dismissed.

The key features of this framework are:

- that it uses a high-level development language (C#) and feature-rich run-time environment;

- that it defines and implements a unique software-based pipeline processing model;

- that it is a flexible and easily adapted object model providing well-defined functional interfaces;

- that it provides an interoperability layer that directly supports integration with 3<sup>rd</sup>-party tools and other external software and hardware.

The end result of attempts to characterize and manage the vagaries of multiple interacting threads is the realization that achieving some measure of real-time software receiver operation will require much more than additional processors and complex algorithm optimizations.

The Receiver Development Framework is the outcome of an analysis process that was an attempt at standing back and taking a holistic view of the overall approach to GNSS receiver application research and development. The significance of this work lies in the establishment of the collection of object models and base implementations for real-time receiver development. Without it, there is a limitation to the degree of improvement to software receiver performance that can be made through individual optimization efforts alone. By adopting the principles and integration philosophies embodied and presented in this work, world-wide efforts can be combined into a unified development model, which has the potential for enhancing researcher productivity through the reduction of redundant non-value-added activities.

#### 1.1 Overview and Background

Global Navigation Satellite System (GNSS) is the general term given to the process of identification of user position through the relative location of known orbiting satellite platforms. There are currently two operational GNSS services: the Global Positioning System (GPS) funded by the US Department of Defense and the Global'naya

Navigatsionnaya Sputnikova Sistema, which translates to Global Navigation Satellite System (GLONASS), developed by the former Soviet Union and now supported by the Russian Federation. Both GPS and GLONASS are operated under the joint control of military and civil agencies.

The European Union (EU) in collaboration with the European Space Agency (ESA) is currently in the process of deploying the **Galileo** satellite-based navigation system.

Galileo is expected to be operated under the control of a civilian agency, but will undoubtedly also be used by military authorities. The Chinese have developed and deployed a regional satellite navigation system known as **BeiDou**, that unlike GPS,

interacts with the user to determine a position estimate. Another Chinese system— Compass or BeiDou-2, similar to GPS, is currently under development.

While the modulation and data encoding methods may differ in their specific implementations, GLONASS and Galileo are largely variations of GPS and share many similarities. As a result, mixed-constellation receivers have been developed that interoperate with navigation data from these systems.

Software Defined Radio (SDR) is a broad term that can apply to the different aspects of transceiver functions. SDR makes use of software digital signal processing (DSP) techniques to create or receive data streams that are converted to/from the analog domain as close as possible to the antenna in the signal path. For a receiver, the intelligence information or message from the carrier is extracted by means of extensive processing in software.

GNSS receivers based on SDR allow a flexible, customizable, and easily extensible solution in which the future requirements for system operation can be altered or updated after the system has been deployed. For example, a multi system, multiple constellation, SDR GNSS receiver could be developed that would allow the resolution of position from a mixed set of visible satellites when there is an insufficient number visible from a single system. A multiple-constellation system can provide higher positioning accuracies than a single constellation system, even when there is a sufficient number of satellite signals available from a single constellation.

The approach most often taken to software-centric signal processing is based on Fourier transform analysis. Large data sets in the time domain are captured from an input

signal sampling hardware device and then converted to the frequency domain through a Discrete Fourier Transform (DFT) or its fast (FFT) alternative. Once in the frequency domain, more complicated operations such as correlation and convolution can be replaced by multiplication. However, this approach is very difficult to make work in a real-time manner, especially at high sample rates and in situations where the signal needs to be processed for more than one data stream from more than one transmitting source. Analyzing signal data in parallel requires either that all tracked sources have access to copies of the incoming data stream, or that they have access to a shared buffering data structure. Maintaining multiple copies of the data can create memory resource issues, and sharing the data requires a synchronized or thread-interlock mechanism that limits peak system performance. Adding to this complexity is the further need of establishing a common reference time base or source that the data demodulators can work from, which serves only to increase the design headaches.

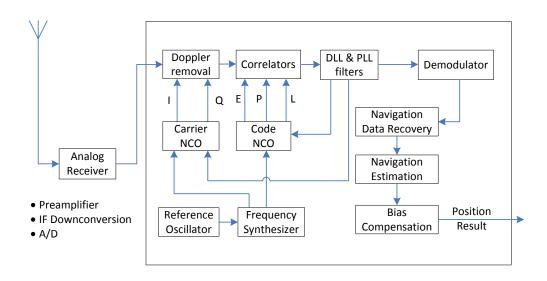

While frequency-transform features have been supplied, the Receiver Development Framework (RDF) takes an adaptable and flexible asynchronous pipeline approach to working with each sample as it arrives in the discrete time domain for most of the signal processing activities. Software representations of block diagrams for hardware-based receiver components can be developed and "plugged in" to the framework pipeline, making the development effort easier and faster. More importantly real-time performance has been considered essential and is achievable with the pipelined approach.

The framework provides implementations of many adaptable pieces that can be used to build a rich variety of functionality. The interoperability features of the framework support the direct integration of custom or commercial hardware and software

components at any point in the processing sequence. As a result, components can be described and simulated using software representations for baseline performance characterizations. Then, hardware versions can be synthesized using an HDL and FPGA toolset using parameters derived from the software components. These hardware pieces can be subsequently connected back into the pipeline, replacing the software component, so that performance comparisons for improvements from the baseline can be made.

Alternatively, existing libraries of software can be directly integrated with the framework for testing without the need to rewrite previously tested code.

The framework was developed and tested with a GPS receiver implementation for measuring the required observables of code and carrier phase, and carrier frequency (Doppler) necessary for a pseudorange measurement. However, extensions to the framework are possible that would make it suitable for a wide range of applications, such as audio/video signal processing and feedback control systems.

The implementation of the framework has been developed using the Microsoft .NET Framework version 3.5 and the C# development language, with some device drivers written in C. However, as described, the framework could be developed in other languages and operating environments. The design is object-oriented, so tools and languages that directly support an object-based development paradigm will be more suitable for future adaptations.

#### 1.2 Previous Work

While a software-only approach to GNSS has been predicted, highly anticipated, and widely researched for some time, only recently has the capability of general purpose

CPUs been up to the required signal processing performance demands. Recent publicly-disclosed SDR GNSS attempts, however, are non-real-time, have specific hardware dependencies, and often work with a single system on a single frequency. Other soft-GPS solutions are proprietary or largely commercial endeavors that poorly support the open environment needed for receiver research.

General background information on the design and operation of GPS receivers can be found in (3) and broader but related details on spread-spectrum communication systems in (4). Additional information on software signal processing methods are provided in (5), (6) and (7). These references develop some of the necessary theory for software-based GNSS receivers.

Many solutions are intended more for modeling the behaviors of individual system functional blocks for hardware implementations, and lack a whole-system approach for performance analysis. Taking a direct block-diagram approach towards receiver design, and then constructing it using iterative frequency-domain transformations, bypasses the opportunity for discrete optimizations and yields non-real-time performance characteristics. Solutions such as (8) possess real-time behaviors, but are based on specialized hardware chipsets, support only GPS, and lack extensibility for dual-frequency support.

Papers such as (9) discuss the current research activities, and provide some guidance to the architectural requirements, but lack documentation on any substantive implementations. The work discussed in (10) is an FPGA-based real-time GPS receiver connected to a PC for graphical display of the results. While solutions that include an

FPGA fabric for signal processing acceleration can be regarded as "reconfigurable," modifications to the systems require non-trivial tools and skills. The limited extensibility of these systems negatively impacts their flexibility for use in future, wider research areas.

Reference (11) uses the SIMD MMX (single instruction multiple data multimedia extensions) instructions on the Intel x86 processor. By using C++ and inline assembler, the code gains a 70% performance improvement—which demonstrates that it is possible with targeted optimizations to achieve the necessary work throughput from a PC processor. However, the implementation does not represent a flexible application framework for GNSS research.

References (5) and (12) are non-real-time projects in that they are offline batchoriented processes, requiring specific proprietary hardware. These are predominantly

MATLAB simulations for functional analysis purposes. The work presented in (13) is a

proprietary library of GPS receiver pieces and not a complete general-purpose solution

framework.

Article (14) describes Galileo acquisition software techniques in a non-real-time environment and no concrete implementation details are provided. (15) represents the development and testing of a hardware simulator using non-real-time software techniques. (16) is also a non-real-time MATLAB GPS simulator for a single satellite signal.

The works of (17) and (18) are hardware-dependent FPGA-based special-purpose solutions and not flexible frameworks for further development. (17) is an attempt to

improve or offset limitations in GPS precision under weak-signal conditions using SDR for time-of-arrival (TOA) corrections, and (18) is a proposed reference implementation of a prototype SDR + FPGA architecture GNSS receiver.

References (2) and (19) develop the mathematical models for digital delay and phase-lock loops (DDLL and DPLL) for use in GPS receivers and present software simulations of the results. In particular, (2) states that the work included a software baseband receiver implementation, but it is developed for a simulated signal only and ignores the effects of the navigation message. The work of (20) was a study on post-processing data from an early unconventional civil GPS receiver, Satellite Emission Range Inferred Earth Surveying (SERIES), and was similar, in some respects, to other such data post-processing efforts at UNB.

Many of the so-called real-time systems have been developed more for real-time signal simulation graphing and plotting functions for the purposes of validation and verification. For others, the real-time performance attribute has never been demonstrated operationally, only modeled and simulated, such as the systems described in (21) and (22).

On-going research at the University of New South Wales (UNSW) Satellite

Navigation and Positioning (SNAP) lab is taking the direction of developing combination

hardware (FPGA) and software (C) receiver implementations (23) that are targeted for a

single hardware configuration.

At the 2008 International GNSS Service (IGS) Workshop in Miami Beach, recommendations made in a presentation by researchers from Cornell University and

University FAF Munich (24) seem to support the need for further development of open software GNSS receivers. The presentation encourages the definition of an IGS-sponsored software receiver and the establishment of an IGS format for exchange of data among software receivers, and identifies the need for benchmark comparisons of software receiver performance to traditional commercial hardware devices.

There are so many software receivers of the post-processing non-real-time variety that a comprehensive evaluation of the nature and characteristics of all of them would be practically impossible. Nearly any programming language that can open a file and perform basic mathematical operations can be used for the development of these projects. A good overview of the current state of software GNSS receivers can be found in reference (25) and issues with their testing protocols and challenges covered nicely in (26).

The variety of MATLAB-based solutions, such as those presented in (16) and included in (5), like the examples provided by (6) and (7), are post-processing receivers and possess no real-time design intentions or characteristics.

There are also highly optimized receiver components that are written in some combination of assembler and C++ claiming real-time performance benefits. However, the designs and methods of implementation of test beds such as (18), or the software defined radio receivers for GPS and GNSS discussed in (10) and (17) are cobbled together from the complex interconnection of hardware dependent system prototyping components. Solutions such as these are difficult to repeat and customize, and it is even

harder to incorporate their presented generalized conclusions into a specific application development and testing environment.

Any relevant discussion on threading, parallelism, and the required level of interprocess communication and data structure synchronization are conspicuously absent from the vast multitude of emerging real-time software receiver implementation papers. In (27), a real-time 12-channel SIMD software correlator is described, but the work does not identify any of the challenges or their solutions for managing the necessary level of processing parallelism.

The contributions and key differences of the work presented in this dissertation from the previously identified literature are that

- it is entirely a software solution, with the exception of the hardware front-end, that does not rely on accelerator devices to function;

- it is an object-oriented solution architecture that defines the generalized set of interfaces and base-class implementations for future receiver development;

- it presents a working view of real-time systems and identifies the issues associated with managing shared resources across multiple processing pathways;

- it establishes a pipeline model for software-based signal-processing work that

can be customized and readily adapted for use in a broad range of signal and

control-related applications.

Most notably, the basis of the reference implementation of the framework is the signal processing methods presented in (5), but with greater consideration given in the

design of the modules and components for how these things will be shared and improved in the future. Rather than merely providing a library of code that others will need to pull apart to extricate and augment, the object-oriented nature of the signal processing pipeline components facilitates a much simpler approach to customization and specialization. Innovative new functionality will be able to be encapsulated in a self-contained assembly that can be made available to other researchers, who will only have to add the components directly to their own projects. The process will eliminate the lengthy setup and build times associated with the configuration of cumbersome non-homogeneous development environments.

# **Chapter 2 GPS Operation**

The known propagation characteristics of radio waves make their use for obtaining position information as valuable as their use for communication. Radionavigation began with the development of Loran (long-range navigation) system during WWII, and subsequently accelerated with the advent of ground-based short-range line-of-sight navigation aids such as the VHF Omni-directional Radio Range (VOR), the Instrument Landing System (ILS), and the Microwave Landing System (MLS) (3).

### 2.1 Trilateration

Estimation of position based on distance measurements to reference points at known locations is called **trilateration**. By measuring the length of time taken for a radio signal to propagate from a transmitter to an observer, combined with the known speed of travel of radio waves, it is possible to determine the distance between the transmitter and the observer. A radionavigation system based on this idea is referred to as a **time-of-arrival** (TOA) system (3).

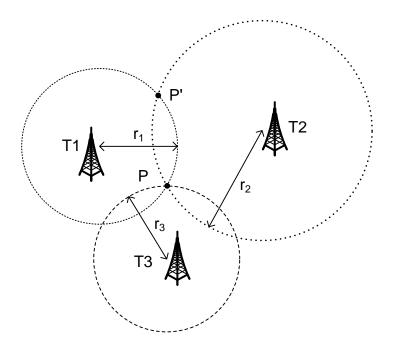

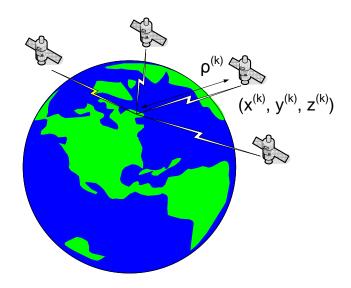

As illustrated in Figure 2-1 [adapted from (3)] if one can determine the distances to three radio wave transmitting towers operating at known locations, then one can unambiguously determine their own position.

Figure 2-1—Trilateration: Determining the range to three transmitters at known locations permits an observer to calculate their position, point P

By measuring their distance, or range, to transmitter T1 with known coordinates, the observer's **line of position** (LOP) must lie on a circle of radius  $r_1$  that is centered on T1. Range information from a second tower T2 gives a circle of radius  $r_2$ , thereby reducing the uncertainty in the observer's actual location to the two points where the circles intersect, P and P'. While it may be possible to reject one of the points based on other physical information, it typically requires finding the range to a third transmitter to unambiguously determine the observer's position, point P.

To extend the system to 3-dimensional solutions, it is necessary that the angle of elevation between at least one of the transmitters and the observer be large (3). Since ground-based transmitters are limited by practical tower heights, the solutions obtained from them are restricted to 2-dimensions. In the case of a satellite-based transmitter, each range measurement would result in an LOP described by the geometry of a sphere, the

surface of which represents a potential area of position. Three intersecting spheres would identify a coordinate in 3-dimensions at or near the surface of the earth.

GPS is a trilateration-based TOA system. In order for a user of the system to make a position determination (position fix) it is necessary that information regarding the nature and orbit of the satellites that are visible to the receiver (in view) be communicated at the time that the fix is made.

At an approximate orbital radius of 26,560 km the GPS satellites move in space at about 4 km/s, yet their positions can be accurately predicted with an error of less than a few meters 24-48 hours in advance (3). The transmission times are imprinted on the signals using *nearly perfect and nearly perfectly synchronized* atomic clocks on the satellites. The precise estimation of the arrival times at the receiver is made possible by spread-spectrum signaling, which allows each satellite to transmit its unique signal on a shared frequency.

### 2.2 System Overview

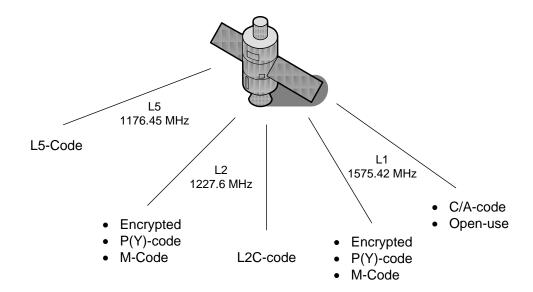

GPS consists of a baseline constellation of at least 24 satellites (they try to keep 30 or more functioning at all times) that operate on the L1:1575.42 MHz, L2:1227.6 MHz, and L5:1176.45 MHz frequencies. All current satellites transmit a public C/A-code (Coarse Acquisition) on L1 and an encrypted P(Y)-code on L1 and L2. Presently, there is only one satellite actively transmitting on L5—full operational capability for the L5 signal is scheduled for 2018 when plans call for 24 L5-capable satellites to be on orbit. The latest generation of satellites, Blocks IIR-M and IIF ("R" is for *replenishment* and "F" is for *follow-on*), additionally transmit a new L2C civil code on L2 (7).

The navigation data transmitted by the satellites are **Binary Phase Shift Keying** (BPSK) encoded at 50 bps and broadcast using a direct-sequence spread-spectrum technique known as Code Division Multiple Access (CDMA) (5).

## 2.2.1 System Architecture

The components of the GPS architecture are organized into three functional groups or segments: the space segment, the control segment, and the user segment. Each segment serves a specific function or describes a particular operation of the complete system.

The **space segment** is where the satellites live. The baseline GPS constellation is comprised of at least 24 satellites that are distributed in six orbital planes inclined 55° to the equator. Each orbit has four primary satellites and room for several spares. The satellites are identified by a letter (A-F) for the orbital plane and a number (1-6) for the order of the satellite within the plane. With an orbital period of approximately 12-hours, the primary 24 satellites cover the earth in such a way that at least four, and possibly as many as 12, are visible at any time (7).

The **control segment** consists of the **Master Control Station** (MCS) located at Schriever Air Force Base in Colorado, with a backup at Vandenberg Air Force Base in California; several unmanned and remotely operated monitor stations spread around the world; and the ground antenna upload stations that receive telemetry from, and transmit commands to, the satellites. The role of the control segment includes monitoring and maintenance of the satellites' health, orbit, and time (GPS Time), and to predict the satellites' orbital information (the ephemerides) and clock parameters that are required by a receiver in order to make position determinations.

The **user segment** is the part of GPS that most people are familiar with, namely the receivers and devices. It is the responsibility of the receiver to identify and track in-view satellites, to detect and decode the navigation message, and to calculate a navigation solution. The unknown difference, or bias, between the satellite clock and that of the receiver is overcome by an additional parameter in the "fix" calculations, shown in Equation 2-3.

## 2.2.2 Signals

GPS uses basically two types of spreading codes and operates currently on the L1 and L2 frequency bands. Support for L5, as previously mentioned, is planned but is not fully operational. L1 contains a civilian-use C/A code and a military-only encrypted P(Y) code, while L2 contains only P(Y). There is now also a civilian code on L2—the L2C—however, a portion of the L2 frequency band is shared with Aeronautical Radiolocation services (ground radar) on a co-primary basis and may be susceptible to interference from non GPS sources (3).

Each satellite is assigned a unique ID code that it uses to identify its signal transmission. In order to make a position determination, a receiver must identify the code and then synchronize a local replica of it for at least three satellites (four are necessary to remove receiver timing biases), and track these signals for eighteen to thirty-seconds.

#### 2.2.2.1 Frequencies

Currently, GPS signals are broadcast on two carrier frequencies that are known as Link-1 (L1) and Link-2 (L2). The frequency of L1 is 1575.42 MHz, and L2 is 1227.6

MHz. These signals are derived from a very accurate atomic clock on board the satellite operating at 10.23 MHz, and can be related to them by:

$$L1 = 154 \times 10.23 \text{ MHz} = 1575.42 \text{ MHz}$$

$$L2 = 120 \text{ x } 10.23 \text{ MHz} = 1227.6 \text{ MHz}$$

When the clock signal is generated, its frequency is adjusted to be slightly lower by  $4.567 \times 10^{-3}$  Hz in order to account for relativistic effects, making the satellite reference frequency 10.229999995433 MHz on the ground before launch, rather than 10.23 MHz. When received by a receiver, the signals should be at the correct frequencies. However, the relative motion between the satellite and the receiver can produce a Doppler shift in the frequencies by as much as  $\pm 5$  kHz (6).

The total radio-frequency power at the transmitter input port on the satellite is approximately 50 W (3), about half of which is allocated to the L1 C/A code. At the receiver antenna, the signal energy is less than the background noise level ( $\approx$  -160 dBW). As with all CDMA-based systems, it is the receiver's ability to reproduce the PRN sequence used by the transmitter that allows for the extraction of the signal buried beneath the noise (3).

Since the GPS satellites all transmit on the same carrier frequencies, there is the possibility that they will interfere with one another. In order to help avoid this interference, it is desirable that all signals appear to have the same power level at the receiver. Otherwise, a strong signal may cause a large cross correlation peak with a weak signal, and the receiver will miss the desired cross correlation peak in the weaker signal

(6). If transmitted isotropically, less power will be seen by a receiver from a satellite low on the horizon than from one directly overhead. Consequently, the satellite antennae are designed to concentrate more signal energy on the edges than in the middle of the beam.

The transmitted signals are BPSK modulated with the 50 bps navigation data and PRN chipping codes. The chip rate (frequency) determines the amount of signal spreading that occurs and creates a transmitted power spectral density, which is often modeled in the form of a  $sinc^2$  function  $\left(\frac{sin\ x}{x}\right)^2$ . The main lobes of the spectrum are located at the carrier frequency  $\pm$  the chipping rate, making the first null-to-null bandwidth equal to twice the chipping rate.

### 2.2.2.2 Spreading Codes

The present constellation of GPS satellites supports the coarse/acquisition (C/A) and the precision (P) codes. The C/A code is a 1023-chip code that is BPSK modulated onto L1 at a rate of 1.023 MHz, which makes the first null-to-null bandwidth of the primary signal lobe 2.046 MHz. With a 1.023 MHz chip rate and length of 1023 chips, the C/A code repeats itself every millisecond.

The P code is modulated at 10.23 MHz, making the main lobe null-to-null width of the spectrum 20.46 MHz. The P code is not directly transmitted but is first encrypted by a W code, the details of which are a classified **US military secret**, to generate the Y code. Referred to as the P(Y) code, it is not directly available to civilian users, and requires access to a cryptographic key that the military will only provide to authorized users (3). Civil dual-frequency receivers exist that acquire P(Y) measurements through sub-optimal semi-codeless techniques.

The P code is generated from two PRN sequences. One sequence is 15,345,000 chips in length, and the other is 15,345,037 chips long. These two numbers have no common factors and are, therefore, relative primes (6). The duration, or period, of the first sequence is 1.5 seconds  $\left(\frac{15,345,000}{10.23\times10^6}\right)$  and the total combined code length of these two sequences is 1.5 x 15,345,037, or 23,017,555.5 seconds—just a bit ( $\approx$  9 hours) longer than 38 weeks.

Instead of using one code for 38 weeks, the P code is reset each week so that only a one-week-long portion is used, allowing for 37 different one-week-long codes. Each of the 32 possible satellite IDs is assigned to a different section of the code, with five sections being reserved for operational uses such as ground transmission. The time of the GPS Week must be known very accurately in order to perform signal acquisition; normally, the precise time is found by first acquiring the C/A code and then, using the known timing relationship between the two, locking onto the P(Y) code (6). The signals and contained codes are summarized in Figure 2-2.

Figure 2-2—GPS Frequencies and Codes: Note that the L5 frequency and the L2C and M codes are only active on some satellites

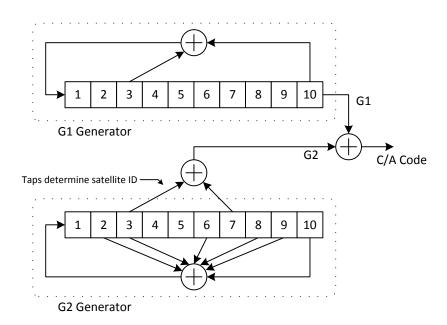

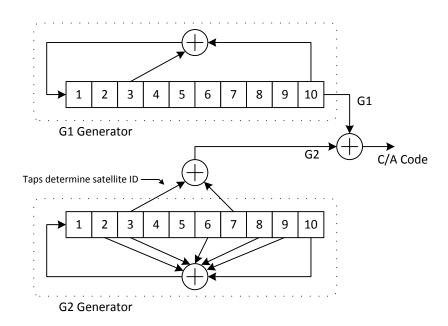

The C/A codes belong to a family of PRN sequences known as *Gold codes*, named after Dr. Robert Gold, that are formed by the product of two maximal length codes, identified as G1 and G2. Gold codes are an important class of periodic PRN sequences that exhibit good periodic cross correlation and autocorrelation properties.

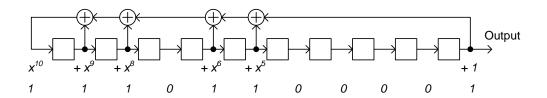

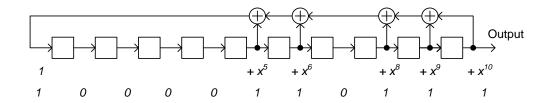

Each code generator is a 1,023-bit sequence formed by a 10-stage maximum length linear shift register that is driven by a 1.023 MHz clock. Maximum-length sequences (m-sequences) can be created by employing modulo-2 feedback from the shift register output and intermediate stages. The feedback tap positions, which determine the output pattern of the sequence, can be expressed as binary polynomials.

The generator function for G1 can be written as  $1 + x^3 + x^{10}$ , meaning the feedback is from bits 10 and 3. The corresponding polynomial for G2 is

$$1 + x^2 + x^3 + x^6 + x^8 + x^9 + x^{10}$$

2-1

so, feedback is from bits 2, 3, 6, 8, 9, and 10 (6).

A pair of taps is taken from stages in G2, modulo-2 added together, and then added to the output of G1 to form the C/A code. The positions of the tapped stages in G2 determine the satellite ID. Initially, all stages of both G1 and G2 are reset to the "1s" condition. Figure 2-3 shows the shift register configuration for satellite ID #2 using the G2 taps 3 and 7.

Figure 2-3—C/A Code Generation: The C/A code is formed by the product of two sequences, G1 and G2

Even though it is 1,023-chips long, when compared with the data rate of 50 bps, the C/A code would be considered a short code; the C/A code is repeated 20 times for each data bit. With a 38 week period, obviously the P code would be a long code. Longer codes with higher chipping rates are more desirable than shorter ones from a positioning

point of view since the length of the code limits the precision of the position that can be determined. Each C/A chip is approximately 1µs wide, which, when multiplied by the speed of light, corresponds to a distance of 300 m. While the signal travel time can be measured to a small fraction of a chip, however in general, the greater the ambiguity in the measurements of arrival time, the greater the uncertainty in positioning (3).

#### 2.2.3 Transmitted Data

The data transmitted by the GPS satellites includes information regarding the health of the vehicle, its key orbital parameters, and the system time. A reduced precision version of orbital data for the entire satellite constellation, called an almanac, is also included to help receivers predict which satellites should be visible into the near future. While only a short amount of signal, about 1 ms, is required to determine which satellites are currently in view, it is necessary to track and demodulate the signal for up to 12.5 minutes in order to receive the entire navigation message, including the almanac, ionospheric correction data, Universal Time offset, and so on.

### 2.2.3.1 Navigation Message

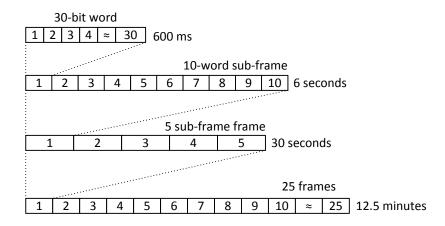

As shown in Figure 2-4, the GPS navigation message is transmitted as words that are 30-bits in length. Ten words make up a sub-frame, and a frame is composed of five sub-frames. At 50 bps, each navigation data bit is 20 ms long, so it takes 600 ms to transmit a word, and six seconds to send a sub-frame. It takes 30 seconds to transmit all five sub-frames of a frame, and the entire message is 25 frames long, repeating every 12.5 minutes (6).

Figure 2-4—GPS Navigation message structure

As previously discussed, essential to the principle of trilateration is the need to know the exact location of the reference transmitters. The precise orbital information for each of the in-view satellites is contained in only the first three sub-frames of each frame of the navigation message, so a minimum of 18 seconds of data is required to accurately determine the satellite's position. However, since the data is being continuously transmitted by the satellite, it is not possible for the receiver to know exactly when these specific sub-frames will be transmitted. To be certain of receiving all three ephemeris sub-frames, it is necessary to wait until all five sub-frames in the frame have been sent. Consequently, 30 seconds of the navigation message, at a minimum, must be recovered to be guaranteed the delivery of sub-frames one through three.

To help ensure error-free recovery of the transmitted navigation message, the data bits are first encoded using a Hamming (32, 26) error detection code (7), meaning for each 32-bits sent, 26 of them are data. Each word in the navigation message contains 30-bits—24 are data and six are parity bits. In order to perform a parity check, eight parity bits are used by incorporating the last two parity bits from the previous word in the

parity-generation algorithm. There are 30 parity generating equations: one for each data bit, and one for each parity bit. Complete details on the data contained in the navigation message are defined in the GPS Interface Specifications (28), while interpretations and explanations can be found in references (5), (3), (6), and (7).

### 2.2.3.2 Ephemerides

Each satellite transmits key orbital parameters in sub-frames 1-3 that a receiver uses to correctly determine its position. These parameters, called an *ephemeris*, are predicted by the Master Control Station based on code and carrier phase measurements at the monitor stations. Parameter sets covering the next fourteen days are uploaded to the satellites daily. The data set that a satellite broadcasts changes every two hours, and without daily refreshing would deteriorate over time (3).

#### **2.2.3.3** Almanac

In addition to its own ephemeris data, each satellite transmits as part of its navigation message, in sub-frames four and five, a catalog of a coarse version of the ephemerides of all satellites in the constellation known as an almanac. The almanac allows a receiver to determine approximately when a satellite will come into view above the horizon given a rough estimate of the user position. The almanac parameters are not required to be as accurate as the ephemeris, and serve only to let the receiver plan when to initiate satellite signal acquisition (3). With PC-based prediction software, users can also utilize the almanac data for observation planning purposes.

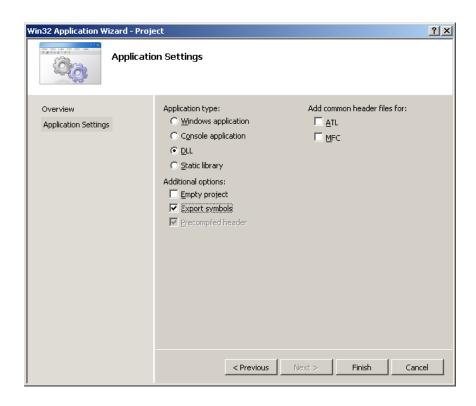

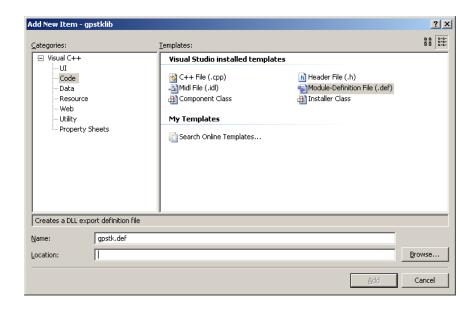

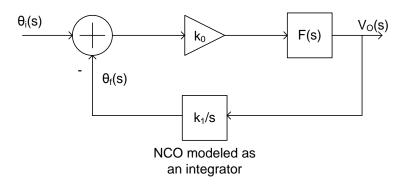

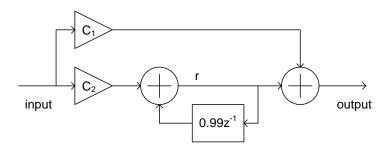

#### 2.2.4 Position Determination